|

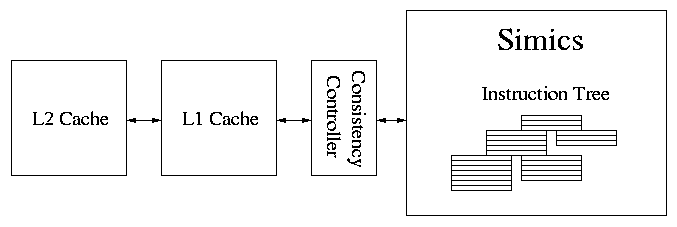

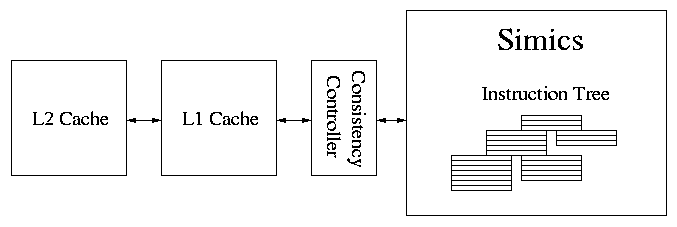

| Figure 3. Consistency Controller |

When simulating multi-processors systems with Simics MAI, you may want to apply a stronger consistency model then the one the LSQ is providing. The consistency controller module provides some default models.

The consistency controller can be controlled through attributes (setting the an attribute to 0 will imply no constraint):

Instructions that issues both loads and stores, e.g. swap instructions, will have both the load and the store status. Thus setting any of the first four attributes will order all such instructions.

The prefetch attribute is orthogonal to all other consistency controller attributes. When not enabled the consistency controller does not issue any memory transaction to the remainder of the memory hierarchy until they are guaranteed to obey the consistency rules. When enabled the prefetch option causes a prefetch to be issued to the rest of the memory hierarchy for all operations where the target address is ready before the consistency controller has guaranteed correctness. As prefetches are nonbinding, it is always correct for any portion of the memory system to ignore them. Note: prefetches are not allowed to stall and they are only sent once for each instruction.

The source code for the consistency controller is available so it is easy to change its behavior in detail. See simics/src/extensions/consistency-controller.