Lecture4 May 12

## **Building an Adder**

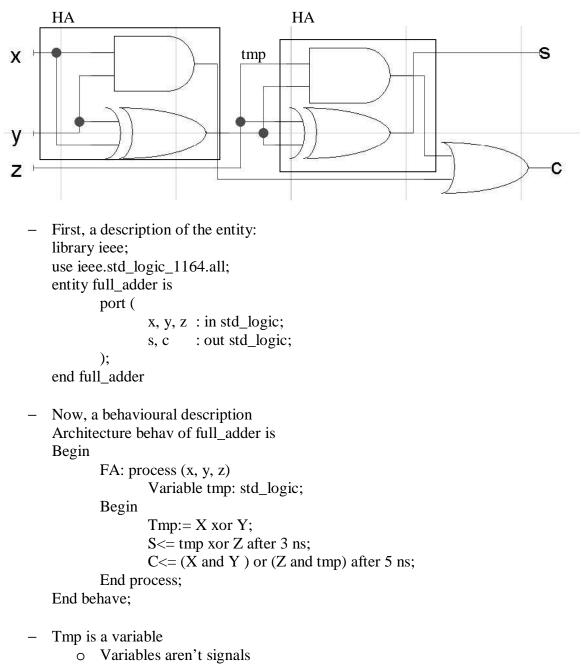

- We will build a full adder

- Used like varabiles in a programming language –to hold info

- Variables have nothing to do w/ structural descriptions or in circuits

- Assignment to a variable is done with := NOT  $\leq=$

- The sequential statements execute in order

- The circuits total  $T_{pol}$  (propogation delay is 5 ns;

- The assignments execute at the same simulation time

- The "after" just delays the result

## - Now, a structural description:

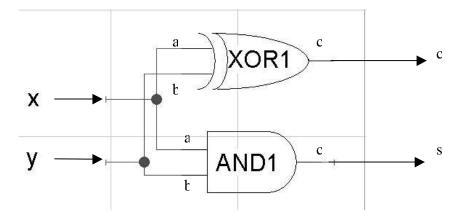

o First, we need gates:

- and\_gate xor\_gate or\_gate o now, we can build a half adder: entity half\_adder is port( x, y: in std\_logic; s, c: out std\_logic ); end half\_adder; architecture struct of half\_adder is begin XOR1: entity work.xor\_gate port map ( a=>x, b=>y, c => s);AND1: entity work.adn\_gate port map( a=>x, b=>y, c=>s); end struct

- "struct" is the name of this implementation

- "XOR1" and "AND1" are the labels for the "entity instance"

- an" instance" is basically a copy of whatever we defined the xor\_gate/and\_gate to be

- the "port map" connects signals in our entity to ports on the instance

- $x \Rightarrow y$  indicates that port x on the instance, y is a signal in the entity we're defining