## **Computer Strucutre**

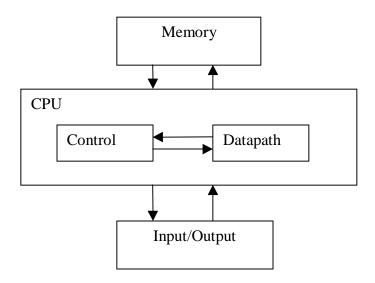

- A generic computer has 4 main units: (fig 1.2)

- A modern processor contains more than just the CPU. Generally:

- o The cpu: fetches & executes operations

- o The FPU (floating-point unit): like CPU, but designed for floating point operations

- o Internal cache: fast memory, used to cache main memory

- o MMU (memory management unit): manages virtual memory

- Not al processor has all of these

- o Embedded system, game machines, tec

## **Circuit Design**

- Combinatorial circuits: outputs depend only on current iinputs

- Sequential circuits: have some kind of memory

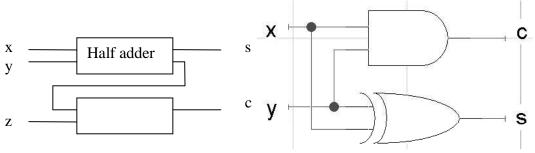

- Hierachial design

- o Design is divided int "blocks" that can be designed separately

- o The works can than be combined

- o If we choose the right blocks, they can be re-used

- ... or they can come pre0defined in libraries

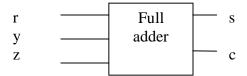

- o a full adder

## **VHDL**

- the "VHSIC hardware Description Language"

- o VHSIC: very high speed intergrated circuits –a US gov't research project

- A standard language w/ many implementations

- o We'll use synopsys

- A language for describing hardware

- o Encourages hierarchial design

- A simple block

- Each block is a VHDL entity

- A VHDL entity should start with these lines

Library ieee;

Use ieee.std\_logic\_1146.all;

(grab these libraries we need)

- Then define the inputs & outputs of the block":

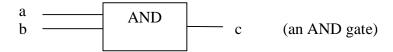

Entity and gate is

port (

a, b : in std.loic; c : out std.logic);

end and.gate;

- Each statement ends with a ";"

- "and gate" is the name of the entity

- "port" gives the list of ports-connections to the outside

- "a,b" are input ports, "c" is an output

- "std.logic" is a signal type that comes with the IEEE library

- signals

- o represents a signal sent along a connection

- o we'll use std\_logic for most signals

- o a std)logic signal can have these values

- '0' 0—false

- '1' 1—true

- 'X' error | unknown

- 'U' uninitialised

- and 4 others